# Plan B: A Buffered Memory Model for Java

Delphine Demange<sup>2</sup> Vincent Laporte<sup>2,1</sup> Lei Zhao<sup>1</sup> Suresh Jagannathan<sup>1</sup> David Pichardie<sup>3,1</sup> Jan Vitek<sup>1</sup>

<sup>1</sup>Purdue University <sup>2</sup>ENS Cachan Bretagne - IRISA <sup>3</sup>INRIA Rennes

#### **Abstract**

Recent advances in verification have made it possible to envision trusted implementations of real-world languages. Java with its type-safety and fully specified semantics would appear to be an ideal candidate; yet, the complexity of the translation steps used in production virtual machines have made it a challenging target for verifying compiler technology. One of Java's key innovations, its memory model, poses significant obstacles to such an endeavor. The Java Memory Model is an ambitious attempt at specifying the behavior of multithreaded programs in a portable, hardware agnostic, way. While experts have an intuitive grasp of the properties that the model should enjoy, the specification is complex and not well-suited for integration within a verifying compiler infrastructure. Moreover, the specification is given in an axiomatic style that is distant from the intuitive reordering-based reasonings traditionally used to justify or rule out behaviors, and ill suited to the kind of operational reasoning one would expect to employ in a compiler. This paper takes a step back, and introduces a Buffered Memory Model (BMM) for Java. We choose a pragmatic point in the design space sacrificing generality in favor of a model that is fully characterized in terms of the reorderings it allows, amenable to formal reasoning, and which can be efficiently applied to a specific hardware family, namely x86 multiprocessors. Although the BMM restricts the reorderings compilers are allowed to perform, it serves as the key enabling device to achieving a verification pathway from bytecode to machine instructions. Despite its restrictions, we show that it is backwards compatible with the Java Memory Model and that it does not cripple performance on TSO architectures.

Categories and Subject Descriptors D.3.1 [Programming Languages]: Formal Definitions and Theory; F.3.1 [Specifying and Verifying and Reasoning about Programs]

**Keywords** Concurrency; Java; Memory Model; Verified Compilation

#### 1. Introduction

Formally verified systems are becoming a reality [18, 20]. Recent successes have shown that it is possible to construct reasonably efficient compilers along with a machine-checked proof of correctness. Building on our experience with the Fiji real-time virtual machine [26] and verified compilation for relaxed memory architectures (CompcertTSO) [35], we have embarked on a project to produce a verified platform for a variant of the Java language that abides by the Safety Critical Specification for Java [12]. To build a verifying compiler requires starting from a formal semantics of the source language and, simultaneously, developing and proving the

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

*POPL'13*, January 23–25, 2013, Rome, Italy. Copyright © 2013 ACM 978-1-4503-1832-7/13/01...\$10.00

**Figure 1. JMM.** x,y and z are shared memory variables,  $r_i$  are local. In the JMM, no execution yields  $r_1=r_2=r_3=1$ . However, manually reordering the writes to x and y so that they are performed in the same order in both branches allows the compiler to eliminate the conditional and hoist the assignments above the store to  $r_1$ , thus making such an execution permissible. Alternative definitions of the JMM [5] allow this execution, but the justification is complex, involving subtle notions of speculations and non-local reasoning over execution traces.

correctness of optimizations and transformations, with an associated formal operational semantics developed for each of the compiler's intermediate representations all the way through to the backend target. Although we expected Java to be a challenge because of the complexity of the transformations used in high-performance virtual machines like Fiji, the Java memory model [22] also complicates the task of devising a tractable formal semantics for the source and intermediate representations.

The Java Memory Model (JMM) was designed to specify the behavior of concurrent programs across all modern architectures and compiler optimizations currently in use in production virtual machines. The complexity underlying the JMM stems from the need to give a semantics to all programs, even racy ones, and the desire to be maximally portable. This degree of generality comes at the price of complexity. When explaining the semantics of racy programs, textbooks [11] elide key JMM notions such as the definition of a legal execution. This issue remains the subject of much active research [4, 5, 10, 15, 21]. Consider Fig. 1 which shows a program where, according to [22], no execution can yield  $r_1 = r_2 = r_3 = 1$ . But, if the programmer were to manually reorder the instructions in the else-branch, a seemingly insignificant refactoring, this result would be allowed. Such unintuitive behavior is unfortunate. From the verifying compiler writer's point of view, the situation is not much better – it is an open problem to write correctness proofs for a compiler with respect to the JMM's current definition, especially if the target platform enforces its own relaxed (or weak) memory semantics. Indeed, even in the absence of formal proofs, existing Java compilers are not JMM compliant [34]. (And in the process of writing this paper we discovered that our own virtual machine was not JMM compliant.)

Often the JMM is informally discussed in terms of allowed instruction reorderings combined with *sequentially consistent* (SC) interleavings. To illustrate, assume for a moment that reordering of independent, non-volatile, statements was allowed, then we could admit  $r_1 = r_2 = 1$  as the value of the program on the left.

This would be true because after reordering, the result is an SC execution. With this approach, reasoning would be easy – determining the validity of an execution would boil down to considering

combinations of permitted reorderings. Unfortunately, the JMM reorderings are complex, and reasoning about transformations is rarely intuitive. To rule an execution illegal requires showing that it is not an SC execution if the program is data-race free, or that it includes an *out-of-thin-air* read. Formalizing these notions leads to a complex definition involving race-committing sequences. This is a level of complexity that is challenging for most programmers to tackle. In [5], four test cases from Pugh et al. [28] were found to be flawed, but a later paper [37], using an automatic verification tool, contradicted this interpretation on two of the examples. Such a lack of clarity for programs less than 10 instructions long does not bode well for the viability of the model.

The complexity of the JMM arises in large part by its desire to be portable across all platforms and thus hardware agnostic. But, this is a challenging goal given the vastly different relaxed memory subsystems found on modern architectures, and the range of optimizations modern compilers perform, many of which are often ill-understood. For example, operational definitions of the Power architecture [31] are substantially different from those defined for x86 [36]; the former supports out-of-order unbounded speculative executions and subtle notions of partial coherence, while the latter is expressed in terms of more intuitive store buffers and limited memory reorderings. It is unclear how one might define a tractable formal language memory model that can be effectively tailored to both. Neither is there a clear specification of the optimizations that ought to be supported.

Of course, we could greatly simplify the problem by drastically limiting the behaviors admitted by Java with an easily understood albeit more restrictive model such as sequential consistency. Valid program executions would be limited to those that can be expressed purely in terms of a sequential interleaving of thread actions; but under SC, reordering of shared-memory reads and writes is prohibited. While simple to state and easy to understand, we choose to not follow this approach because SC would likely cripple performance of Java programs on all modern microprocessors due to the large number of fences needed to enforce SC on relaxed hardware; this would be especially true for racy programs implementing sophisticated lock-free algorithms of the kind found, for example, in optimized libraries such as java.util.concurrent.

Instead, we propose an alternative memory model that has a tractable semantics and designed to be mapped to x86 multiprocessors that support a Total Store Ordering relaxed memory semantics [30, 36]. We introduce the Buffered Memory Model (BMM), a memory model for Java that can be fully characterized in terms of the memory reorderings it allows on top of sequentially consistent executions. The BMM comes in two forms. The first is an axiomatic specification that can be used to relate it to the JMM, and which provides an intuitive method to describe valid and invalid program executions. The second form is a fully operational abstract machine with write buffers attached to each thread. This semantics can be readily used by a verifying compiler infrastructure like CompcertTSO. BMM is backwards compatible: existing software that has been written against the JMM can be run directly since the JMM is a superset of the BMM (i.e., every legal BMM execution is legal under the JMM). This ensures that legacy software that has been validated and tested with the JMM in mind will remain correct. The contributions of this paper are thus as follows:

- An axiomatic definition of the BMM, an alternative memory model for Java programs, fully characterized in term of memory event reorderings, and a compliance proof with the JMM.

- A formalization of BMM<sub>o</sub>, an operational definition of the semantics of Java programs, equipped with a simple mapping to the Total Store Order (TSO) memory model enabling it easily be used with the x86 family of multiprocessor architectures

- and with verified compilers like CompcertTSO targeting such platforms.

- A proof that BMM and BMM<sub>o</sub> are equivalent. We prove the data race freedom (DRF) theorem for BMM and the legality of reordering optimizations under the BMM.

- An upper bound on the cost of preserving BMM semantics on a production virtual machine running on a TSO hardware, benchmark results measuring the cost and overhead of BMM enforcement, compared to JMM-compliant implementations, and an illustration of the subtle performance implications of the memory model with a case study on the implementation of biased locking.

We note that the design rationale for the BMM is very much dictated by our overarching goal of constructing a verifying compiler for Java. As a result, BMM is not intended to be general-purpose, and does not apply directly to all architectures and compiler optimizations. Instead, we view it as a starting point for further research on verified compilation and memory models.

The BMM, the statements of results and key lemmas are expressed in Coq; our proofs are rigorous but non-mechanised. The details are available online, along with the version of Fiji and LLVM used in our benchmarks: http://r.cs.purdue.edu/bmm

#### 2. Related Work

Language Memory Models. Languages like Java and C++ have sophisticated memory models to answer questions related to data visibility and updates for concurrent programs. The JMM does this using committing-sequences, that make it subtle, complex, and unsound [10, 34]. Huisman and Petri [15] proved its DRF guarantee. They tackled the inconsistencies of [22], related to memory initialization by adding hypotheses. Aspinall and Ševčík [5] proposed an alternative definition of the JMM that does not suffer from these issues. They restrict their definition to the finite case, as we do here. Recently, Lochbihler [21] extended the formalization by including infinite executions and dynamic allocations. This work proves type-safety for correctly synchronized programs. Such a mechanized proof is a tour de force since it covers a large fragment of Java. However, the proof structure is quite different from the simulation proof we need to perform within the scope of a verified optimizing compiler. There has also been recent work on memory models for C++. Boehm and Adve [6] provide a semantics for datarace free C++ programs, including a semantics for *low-level atomics*. In Java, it is mandatory to also give well-defined semantics to racy programs to avoid security breaches.

Weak Memory Model Formalizations. Work in this area has focussed primarily on characterizing hardware memory models. Early studies [1, 2, 13] outlined a range of hardware memory models, and attempted to rigorously formalize the vendor's documentations. Alglave et al. [3] defined a general framework for formalizing hardware models using partial orders. Operational characterizations have been examined in [25, 30, 31]. Burckhardt et al. [9] define an expressive denotational framework where a memory model is a set of dynamic reorderings, aggregation or splitting rewriting rules. TSO boils down to a store-load reordering and a store-load aggregation rule. The BMM follows this line of work by providing provably equivalent axiomatic and operational models that make it intuitive and suitable to verification.

**Proofs, Verified Compilation, and Weak Memory Models.** Defining multithreaded semantics in terms of reordering is also the approach taken by Miné [24]: the semantics of multithreaded C programs is defined as the interleavings of the programs possibly obtained by the syntactic transformations defining the memory model.

From a certified compiler perspective, an operational definition of the JMM is desirable. There are several attempts to provide such a semantics [7, 8, 10, 16] but none of them has been used in a proof assistant. Our operational semantics is inspired by the TSO memory model proposed in [35] which has been formalized in Coq. Ševčík [32] identifies some trace transformations that are valid under the JMM. Transformations are however defined semantically. This gap is filled in [33] where the program transformations are proved to be correct, but this is done under a DRF assumption. [33] also identifies the need for characterizing memory models in terms of the transformations they permit, and this is the goal of the axiomatic formalization of BMM.

# 3. BMM: Two Models for the Price of One

While the BMM covers the whole of Java, the most challenging parts of reasoning about concurrent programs are those that manipulate shared memory in a potentially racy way. Following the JMM's design, we separate operations that are purely thread-local from those that deal with shared memory. The BMM is parametrized by an abstract notion of intra-thread semantics to deal with the former. We mention a few of the high-level concepts and our design choices before focusing on the memory model proper. (More details about this part of our model is in the online Coq development.)

**Java Values.** The JVM operates on two kinds of values: primitives and references. Primitives include long and double values that are 64-bits wide. Updates to these variables is not guaranteed to be atomic on a 32-bit machine. Our intra-thread semantics captures this. The treatment of references is delicate. Several instruction like instanceof, checkcast, invokevirtual require reading the class of an object pointed to by a reference. These operations are not relevant to the memory model because they refer to immutable meta-data. We explicitly avoid reading from shared memory in those cases since that would directly entail reasoning about the memory model. Instead, our semantics attaches type information to references in the spirit of formalizations of the bytecode verifier. As a consequence, the type of an object can be conceptually read without going to shared memory. We also give to each thread its own allocation pool. This matches the notion of field initialization that is advocated in the JMM. We do not need to initialize objects with a default value when we allocate them because each memory address has a well-typed initial value from the very beginning of the program execution.

Final Fields. The JMM provides complex rules for fields annotated final. Compilers are allowed to perform aggressive optimizations on reads. The surprising thing is that final fields may change between reads. This occurs if the programmer leaks an object during its construction. The result is a very non-intuitive semantics which stands more as a warning for the programmer who does not follow a safe publication pattern than a real semantics. Our position is to forbid unsafe publications [14] (which happens to be a restriction imposed by Safety Critical Java as well). This allows us to keep an intuitive semantics for final fields and let compilers aggressively optimize them.

*Class Initialization.* Lazy class loading is an important mechanism for concurrent programming; see for example the *initialization on demand holder idiom* [27]. Our semantic supports this by tracking the current initialization status of each class.

Synchronization Actions. Their treatment in the paper is slightly simplified. Our formal semantics needs to handle more synchronization actions than those explained here. For example, when spawning a thread, an exception IllegalThreadStateException can occur if the thread has already been started. It means that, for a

given execution and a given thread, there can be only one successful spawn event but several other failed spawn events. A so-called JMM *synchronizes-with* edge must exist between the successful spawn and all failed spawn events.

#### 3.1 A Reordering-based Memory Model

We propose a memory model that can be *fully* characterized by reorderings over SC executions and that has a simple specification. In the BMM, (1) all SC executions are allowed and, (2) any execution from which an SC execution can be derived by reordering a non-volatile read action with a preceding non-volatile write action is allowed; both actions must operate over disjoint memory locations and the actions can be separated by a sequence of reads that see the write action. Thus, for instance in the following program

$$\begin{array}{c|c} x \leftarrow 0 & y \leftarrow 0 \\ \hline x \leftarrow 1 & y \leftarrow 1 \\ r_1 \leftarrow y & r_2 \leftarrow x \\ \hline r_1 = r_2 = 0 \text{ is allowed} \end{array}$$

it suffices to reorder one of the threads for the result to be permissible under an SC execution. Fig. 2 gives some prohibited executions. Thanks to this reordering-based definition, all three examples are easily seen to be illegal since no reordering is applicable and no SC execution can exhibit such behaviors.

$$\begin{array}{c|c} x \leftarrow 0 & y \leftarrow 0 \\ \hline x \leftarrow 1 & r_1 \leftarrow y \\ y \leftarrow 1 & r_2 \leftarrow x \\ \hline r_1 = 1, r_2 = 0 \text{ is illegal} \end{array} \qquad \begin{array}{c|c} x \leftarrow 0 & y \leftarrow 0 \\ \hline x \leftarrow 1 & r_1 \leftarrow x & r_2 \leftarrow y \\ \hline y \leftarrow 1 & r_3 \leftarrow x \\ \hline r_1 = r_2 = 1, r_3 = 0 \text{ is illegal} \end{array}$$

$$\begin{array}{c|c} x \leftarrow 0 & y \leftarrow 0 \\ \hline \hline x \leftarrow 1 & r_1 \leftarrow x & y \leftarrow 1 & r_3 \leftarrow y \\ \hline x \leftarrow 1 & r_2 \leftarrow y & r_4 \leftarrow x \\ \hline r_2 = r_4 = 0, r_1 = r_3 = 1 \text{ is illegal} \end{array}$$

Figure 2. BMM executions.

# 3.2 A Buffered Operational Memory Model

While more intuitive for the programmer, the reordering-based definition of BMM lacks an operational form. What we seek with an operational model is a companion proof technique to provide a formal correspondence proof between the different layers of a verified compiler. Operational semantics have been long advocated as a vehicle within which to conduct such proofs by facilitating the use of simulation diagrams. Thanks to their inductive form, they can be used to reason about global program behavior in terms of elementary single steps. Axiomatic models generally do not enjoy the same kind of proof technique. In [34], to prove validity of some program transformations, the authors had to reason on whole prefixes of traces. This uncomfortable situation comes from the fact that in the JMM, a trace of n+1 execution steps is not easily defined in term of its n first steps. At the hardware level, operational semantics have been provided in [31, 36]. It is not surprising to see that no proof connects the JMM with any of these operational models. Thus, our second memory model, called BMM<sub>o</sub>, introduces a store buffer: each hardware thread effectively has a FIFO buffer of pending memory writes, so that reads performed on different processors can occur before writes have propagated to main memory.

#### 3.3 Reconciling the Two Models

While the axiomatic form of BMM has an intuitive definition and supports a subset of the executions permitted by the JMM, its operational variant has been specified to fit cleanly within the store

|                                 | SC       | C++      | JMM       | BMM       |

|---------------------------------|----------|----------|-----------|-----------|

|                                 |          |          |           |           |

| DRF theorem                     | ✓        | ✓        | <b>√</b>  | ✓         |

| Reordering memory accesses      | ×        | ✓        | ✓         | $\otimes$ |

| Redundant memory accesses       | ./       | ./       | Φ.        |           |

| elimination/introduction        |          |          | ₩         |           |

| Operational semantics           | ✓        | ✓        | ×         | ✓         |

| Semantics for all programs      | ✓        | ×        | ✓         | ✓         |

| Programmer can understand the   | /        | ×        | ×         | /         |

| semantics of racy programs      |          | _ ^      | _ ^       |           |

| Sound with respect to JMM (does |          | ×        | ./        | /         |

| not break legacy Java)          |          | _ ^      | <b>V</b>  | •         |

| Lock optimizations              | <b>√</b> | <b>√</b> | $\otimes$ | $\otimes$ |

**Table 1.** Expressivity and properties of memory models.  $\checkmark$  if a property holds,  $\times$  if it does not, and  $\otimes$  if there are restrictions. The models differ in the reordering they permit, how they are formalized, the programs they consider, and their support for legacy code. BMM is weaker than the JMM in terms of allowed reorderings, but its operational semantics is useful for verifying compiler optimizations, and its simpler axiomatic version is easier for programmers to understand. Reordering memory accesses is illegal under original JMM [10, 22] but legal under the alternative version of [34].

buffering operations provided by x86-based relaxed memory hardware. The two models are reconciled with an equivalence proof. For this purpose, the BMM reorderings have been carefully chosen to align with the behaviors permitted under BMM<sub>o</sub>. These two semantics have different uses. In Sec. 5.1, we use the reordering view to prove the JMM compatibility. In Sec. 8 we use the operational semantics to study the validity of compiler-driven program transformations. Tab. 1 gives an overview of the properties of the BMM.

# 4. Background on the Java Memory Model

We introduce key notions from the JMM. A language memory model formally specifies what values can be read by each thread depending upon the writes performed by this thread or others. These interactions are categorized using inter-thread actions.

Inter-thread Actions. The shared memory of a program is split into a set of disjoint addresses which are instance fields, static fields or array positions but not local variables. For each address  $x \in \mathbb{X}$ , we can determine if it is volatile or not with the function volatile:  $\mathbb{X} \to \text{bool}$ . In the literature, external actions are distinguished from other memory actions. In this work, we model external actions using volatile writes  $^1$ , that can be identified with the function external:  $\mathbb{X} \to \text{bool}.^2$  We assume a set  $\mathbb{T}$  of threads, a set  $\mathbb{L}$  of locks, and a set  $\mathbb{V}$  of values. The set of inter-thread actions is given below, where superscript i denotes the unique identifier of memory actions.

Action  $w_0x$  initializes address x; it has no emitting thread. Thread start  $(b_t)$  and end  $(e_t)$  can happen only once and thus do not require identifiers. For any action a that is not a default write action, we write T(a) the emitting thread of this action. For any write action w, we write V(w) the value written by that action; initialization actions write a default value according to the type of the related address. We use some notations for sets of actions:

$$\begin{split} &\mathbb{A}_{\mathbf{r}} = \{ \mathsf{r}_t^i x \mid t \in \mathbb{T}, \ x \in \mathbb{X} \} & \text{(reads)} \\ &\mathbb{A}_{\mathbf{w}} = \{ \mathsf{w}_t^i x, v; \mathsf{w}_0 x \mid t \in \mathbb{T}, \ x \in \mathbb{X}, \ v \in \mathbb{V} \} & \text{(writes)} \\ &\mathbb{A}_{\mathbf{d}} = \{ \mathsf{w}_0 x \mid x \in \mathbb{X} \} & \text{(initializations)} \\ &\mathbb{A}_{\mathbf{b}} = \{ \mathsf{b}_t \mid t \in \mathbb{T} \} & \text{(begins)} \\ &\mathbb{A}_{\mathbf{s}} = \{ \mathsf{w}_t^i x, v; \mathsf{r}_t^i x \mid t \in \mathbb{T}, \ x \in \mathbb{X}, \ \text{volatile}(x) \} \\ & \cup \{ \mathsf{l}_t^i l; \mathsf{u}_t^i l \mid t \in \mathbb{T}, \ l \in \mathbb{L} \} & \text{(synchronizations)} \\ & \cup \{ \mathsf{s}_t t'; \mathsf{b}_t; \mathsf{j}_t^i t'; \mathsf{e}_t \mid t, t' \in \mathbb{T} \} \\ &\mathbb{A}_{\mathbf{x}} = \{ \mathsf{w}_t^i x, v \mid t \in \mathbb{T}, \ \text{external}(x) \} & \text{(external actions)} \end{split}$$

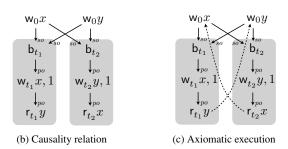

The JMM is based on a *happens-before* model [19]. An execution is described in terms of partial orders between memory actions. The same external behavior may be associated with many different interleavings of thread actions. An interleaving can be seen as a total order on actions: "this action occurs before that one according to global time". Such an interleaving is in fact a consistent extension of a partial order called "happens before" that precisely relates causal dependencies between actions. For example, the program Fig. 3a may exhibit an interleaving of thread-actions

$$\mathsf{b}_{t_1} :: \mathsf{b}_{t_2} :: \mathsf{w}_{t_1} x, 1 :: \mathsf{r}_{t_1} y :: \mathsf{w}_{t_2} y, 1 :: \mathsf{r}_{t_2} x$$

but there is no causal dependency between the read performed in  $t_1$  and the one performed in  $t_2$ . Fig. 3b presents the causality relation behind such a linear presentation. Each gray region is dedicated to the actions owned by a same thread.

$$\begin{array}{c|cccc}

x \leftarrow 0 & y \leftarrow 0 \\

\hline

x \leftarrow 1 & y \leftarrow 1 \\

r_1 \leftarrow y & r_2 \leftarrow x

\end{array}$$

(a) Code of threads  $t_1, t_2$ .

**Figure 3.** Happens-before execution with and without write-seen arrows.

The unique identifier is omited here. Any sequence of solid arrows between actions a and b means a should happen before b. Apart from address initialization and thread starts, few actions are actually constrained in this example. We distinguish two kinds of arrows:  $\stackrel{po}{\longrightarrow}$  reflects program order between actions of a same thread;  $\stackrel{so}{\longrightarrow}$  reflects the synchronization relation between events. In more complex

$<sup>\</sup>overline{}$  E.g., a call by a thread t to a function f with arguments args that returns value  $\vee$  is modeled as a volatile write to the abstract location f(args).

<sup>&</sup>lt;sup>2</sup> We require that,  $\forall x$ , external $(x) \Rightarrow \text{volatile}(x)$

<sup>&</sup>lt;sup>3</sup> Unlike [5, 22], we stick to the JMM: every address is virtually given a default value at the start of the program, even if the corresponding location is not allocated yet.

examples, it may relate an unlock of a monitor with its subsequent lock or the write of a volatile address with a subsequent read. Dotted arrows indicate which write was seen by each read action. These arrows form what we call an axiomatic execution. The write seen must satisfy some minimal constraints that we will make clear with the notion of well-formed execution.

**Notations.** When a partial order is total we write it directly as a sequence of elements that uniquely characterizes it. When a partial order  $\stackrel{o}{\to}$  is a disjoint union (indexed by  $\mathbb{T}$ ) of orders, we write its restriction on thread t as  $[\stackrel{o}{\to}]_t$ . A list of elements can be thought of as a total order. We write  $a \stackrel{tr}{\to} b$  when elements a,b are ordered with regards to a list tr. We call any irreflexive transitive relation an *order*. Two such relations R and R' are said to be *consistent* when they satisfy:  $\forall x, y, \neg (xRy \land yR'x)$ . We write  $tr \downarrow_A$  for the sequence tr filtered to the elements of the set A.

DEFINITION 4.1 (Axiomatic execution). An execution E is described by a tuple  $E = \langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle$  where:

- P is a program and  $A \subseteq \mathbb{A} \setminus \mathbb{A}_d$  is a set of actions,

- • po ∴ ⊆ A × A is the program order, a disjoint union of total orders on actions of each thread,

- $\stackrel{so}{\longrightarrow} \subseteq (A \cup \mathbb{A}_d) \times (A \cup \mathbb{A}_d)$  is the synchronization order: the union of a total order on  $A \cap \mathbb{A}_s$  of all synchronization actions in A, and the cartesian product  $\mathbb{A}_d \times (A \cap \mathbb{A}_s)$ ,

- W ∈ A<sub>r</sub> → A<sub>w</sub> is a write-seen function that maps each read action r from A to a write action w of A ∪ A<sub>d</sub> (r and w must operate on the same address).

We now explain how to extract the happens-before relation from the program order and the synchronization order of an execution.

DEFINITION 4.2 (Synchronizes-with relation). An action a synchronizes-with an action b (written  $a \xrightarrow{sw} b$ ) in an execution  $E = \langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle$  if  $a \xrightarrow{so} b$  and a, b satisfy one of the following conditions:

- $a \in \mathbb{A}_d$  and  $b \in A \cap \mathbb{A}_b$  (default writes synchronizes-with starts),

- a is a spawn of a thread t and b is the start of the thread t,

- a is a write to a volatile address x and b is a read from x,

- a is an unlock on monitor l and b is a lock on monitor l,

- a is the end of the thread t and b is a join action on t.

DEFINITION 4.3 (Happens-before order). The happens-before order of an execution is the transitive closure of the union of its synchronizes-with relation and its program order.

$$\xrightarrow{hb} = (\xrightarrow{sw} \cup \xrightarrow{po})^+$$

*Intra-thread Semantics.* Our formalization requires an abstract notion of intra-thread semantic state  $State_{intra}$  and an intra-thread labeled transition relation

given to each thread  $t \in \mathbb{T}$ . Transition labels are in the set  $\mathrm{Label_{intra}} = (\mathbb{A} \setminus \mathbb{A_r}) \cup (\mathbb{A_r} \times \mathbb{V}) \cup \{\tau\}$ : a thread can either take an action step, or a silent step (with label  $\tau$ ) that is memory irrelevant. For a read action step, the value read is paired with the action in the label. The requirements on the intra-thread semantics are:

- ——» only relates states of the same thread,

- there is an *initial* state Ready: no transition leads to it and a thread t steps from it if and only if it emits the b<sub>t</sub> action,

- · non-silent labels are tagged with the emitting thread,

there is a *final* state Done: a step of a thread t leads to it if and only if its last transition is labeled by e<sub>t</sub>.

DEFINITION 4.4 (Intra-traces). Let  $tr=a_1:\dots :a_n$  be a sequence of actions in set A and let W be a write-seen function on A. Given a thread  $t\in \mathbb{T}$  in program P, tr is an intra-trace of t if there exist  $s_0, s_1, \dots, s_m \in \operatorname{State}_{\operatorname{intra}}(m \geq n)$  and  $l=l_1:\dots:l_m \in \operatorname{list}(\operatorname{Label}_{\operatorname{intra}})$  such that:

- for all  $a \in \{a_1, ..., a_n\}, T(a) = t$ ,

- $s_0$  is the initial intra-thread state Ready,

- for all  $i \in \{1, \ldots, m\}$ ,  $s_{i-1} \xrightarrow{l_i} s_i$ ,

- the projection  $b_1 :: \cdots :: b_n$  of l to non-silent labels is such that  $b_i = (a_i, V(W(a_i)))$  if  $a_i$  is a read action or  $b_i = a_i$  otherwise.

We write P[t] for the set of such pairs (tr, W) for P.

DEFINITION 4.5 (Well-formed execution). An execution  $\langle P, A, \stackrel{po}{\longrightarrow}, \stackrel{so}{\longrightarrow}, W \rangle$ , is well-formed if

- A is finite,

- $\xrightarrow{so}$  is consistent with  $\xrightarrow{po}$ ,

- Locking is proper: for all lock actions  $l_i^t l \in A$  and all threads t' different from the thread t, the number of lock actions on l emitted by t' before  $l_i^t l$  in  $\stackrel{so}{\longrightarrow}$  is the same as the number of unlock actions on l emitted by t' before  $l_i^t l$  in  $\stackrel{so}{\longrightarrow}$ , and each unlock action  $u_i^t l \in A$  occurs after a matching lock action:

$$\begin{split} \forall \mathbf{l}_t^i l, \forall t' \neq t, |\{\mathbf{l}_{t'}^j l \mid \mathbf{l}_{t'}^j l \overset{so}{\longrightarrow} \mathbf{l}_t^i l\}| &= |\{\mathbf{u}_{t'}^j l \mid \mathbf{u}_{t'}^j l \overset{so}{\longrightarrow} \mathbf{l}_t^i l\}| \\ \forall \mathbf{u}_t^i l, |\{\mathbf{l}_t^j l \mid \mathbf{l}_t^j l \overset{po}{\longrightarrow} \mathbf{u}_t^i l\}| &> |\{\mathbf{u}_t^j l \mid \mathbf{u}_t^j l \overset{po}{\longrightarrow} \mathbf{u}_t^i l\}| \end{split}$$

- $\xrightarrow{po}$  is intra-thread consistent: for all thread  $t \in \mathbb{T}$ ,  $([\xrightarrow{po}]_t, W) \in P[t]$ ,

- $\stackrel{so}{\longrightarrow}$  is consistent with W: for every read r of a volatile address x we have  $W(r) \stackrel{so}{\longrightarrow} r$  and for any write w to x different from W(r), either  $w \stackrel{so}{\longrightarrow} W(r) \stackrel{so}{\longrightarrow} r$  or  $W(r) \stackrel{so}{\longrightarrow} r \stackrel{so}{\longrightarrow} w$ ,

- $\xrightarrow{hb}$  is consistent with W: for all reads r of x,  $r \xrightarrow{hb} W(r)$  does not hold and there is no intervening write w to x, i.e. such that  $W(r) \xrightarrow{hb} w \xrightarrow{hb} r$ .

A distinguished subfamily of well-formed executions is the set of Sequentially Consistent axiomatic executions.

DEFINITION 4.6 (Sequentially Consistent (SC) execution). A well-formed execution  $E = \langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle$  is SC if there exists a total order  $\xrightarrow{to}$  on A such that

- $\xrightarrow{to}$  is consistent with  $\xrightarrow{po}$  and  $\xrightarrow{so}$ ,

- for each read action  $r \in A$  accessing address x, W(r) is the last write on x before r in  $\xrightarrow{to}$ .

The set of well-formed executions of a program forms the *Happens-Before* memory model. It is relatively easy to manipulate but it is not a satisfactory memory model because it allows *out-of-thin-air* values [22] and does not fulfill the DRF theorem. The JMM considers a subset of this model; these are known as *legal* executions. The exact definition of legal executions is subtle. In a nutshell, a well-formed execution E is legal if there exists a sequence  $E_0, E_1, \ldots, E_n = E$  of well-formed executions such that in  $E_0$ , each read sees a write that it does not race with. Then progressively, each execution  $E_i$  allows some reads through data races but in a well-founded order until the execution E itself is reached. Thanks to this definition, one obtains almost directly that: in a DRF program all reads see writes that happen-before them and each execution is

sequentially consistent; and no out-of-thin-air value can be read, by the causality order on races.

Whereas the DRF guarantee of the JMM is easily achieved, the complex definition of the race-committing sequence makes it hard to justify whether a given reordering is allowed or not. Our approach is to define the BMM with explicit reorderings, introduced in the next section.

# 5. BMM: An Axiomatic Memory Model

We now formally define the axiomatic view of our memory model. The semantics is built on top of two simple notions: sequential consistency and reordering of actions. The transformations of executions are expressed with the notion of local reordering.

DEFINITION 5.1 (Local reordering). Given an execution  $E = \langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle$ ,  $E' = \langle P', A, \xrightarrow{po'}, \xrightarrow{so}, W \rangle$  is a local reordering of E from an action list l to a list l' in thread t if

- $[\xrightarrow{po}]_t = \alpha \cdot l \cdot \beta$  and  $[\xrightarrow{po'}]_t = \alpha \cdot l' \cdot \beta$ ,

- $[\xrightarrow{po}]_{t'} = [\xrightarrow{po'}]_{t'}$  for all threads  $t' \neq t$ ,

- for all  $(tr, W) \in P'[t]$  where tr is of the form  $\alpha \cdot l' \cdot \beta$ , there exists  $(\alpha \cdot l \cdot \beta, W) \in P[t]$ ,

- P[t'] = P'[t'] for all thread  $t' \neq t$ ,

- l and l' contain the same set of actions,

- no element of l or l' is a synchronization action.

Such a reordering is written  $E \xrightarrow{t:[l \longrightarrow l']} E'$ .

Intuitively, we reorder the intra-thread trace  $[\stackrel{po}{\longrightarrow}]_t$  by transforming l into l'. BMM exposes two reorderings to the programmer. The first one is a *Write-Read* reordering which reorders a read before a previous adjacent write to a different address. Here is a simple example:

$$x \leftarrow 1; r \leftarrow y \xrightarrow{\text{WR}} r \leftarrow y; x \leftarrow 1$$

DEFINITION 5.2 (Write-Read reordering). A Write-Read reordering,  $E \xrightarrow{\mathrm{WR}} E'$ , of an execution  $E = \langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle$  with respect to actions w and r in t, is a local reordering E' such that

$$E \xrightarrow{t:[w::r \longrightarrow r::w]} E'$$

where w and r operate on different addresses.

Fig. 4 illustrates the use of the Write-Read reordering on a classical litmus test program. To understand the BMM semantics, a key observation must be made: the execution on the left is not sequentially consistent but after two WR reorderings we obtain a sequentially consistent execution. It is then tempting to ask if a BMM execution is any execution that can be transformed into an SC execution after

Figure 4. Write-Read reordering example.

some WR reorderings. Unfortunately, such a definition would not allow us to capture executions exhibited by TSO-hardware, so we need to work a bit harder.

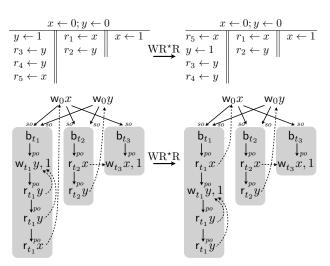

The program on the top-left part of Fig. 5 illustrates this issue. In this program, the configuration  $r_1 = 1, r_2 = 0, r_3 = 1; r_4 = 1, r_5 = 0$  is reachable under a TSO architecture, but it is not a SC execution and no WR reordering can be applied to this program. We introduce a second category of reorderings that is allowed in BMM that permits such executions.

Figure 5. Write-Read-Read reordering example.

DEFINITION 5.3 (Write-Read-Read reordering). A Write-Read-Read reordering of  $E = \langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle$  w.r.t. a tuple of action  $(w, \vec{r}, r')$  of A, is a local reordering E' such that

$$E \xrightarrow{t:[w::\vec{r}::r'\longrightarrow r'::w::\vec{r}]} E'$$

Reads in  $\vec{r} = r_1, \dots, r_n$  have w as write-seen, and r' and w target different addresses. Such a reordering is written  $E \xrightarrow{WR^*R} E'$ .

In Fig. 5, we apply this transformations to the previous program. This time, a reordering is possible and leads to an SC execution. Note that  $WR^{\star}R$  is a generalization of the previous WR reordering. We prove in Sec. 7 that this new reordering exactly captures a TSO operational semantics. Formally, a BMM execution is any execution that can be transformed using  $WR^{\star}R$  reorderings until reaching an SC execution.

DEFINITION 5.4 (BMM executions). BMM executions are:

$$\mathsf{BMM} = \left\{ E \mid \exists E', E \xrightarrow{RO} E' \ \textit{and} \ E' \textit{is} \ \mathrm{SC} \right\}$$

with

$$\xrightarrow{RO} = (\xrightarrow{WR^*R})^*$$

.

We write  $\mathsf{BMM}(P)$  for the set of executions of a program P. The  $\mathsf{BMM}$  observable behaviors of a program P is then defined as the set of sequences of external actions:

$$Obs(P) = \left\{ \xrightarrow{so} \downarrow_{\mathbb{A}_{\mathbf{X}}} | \langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle \in \mathsf{BMM}(P) \right\}$$

The definition of BMM is a least post-fixpoint. Every time we must prove that BMM is included in some set of well-formed executions, we can rely on the following characterization.

LEMMA 5.1 (BMM least post-fixpoint characterisation). BMM is the least set S of well-formed executions such that

- all SC executions are in S,

- S is backward-closed by BMM reorderings: for any well-formed executions E, E' such that  $E \xrightarrow{RO} E'$ , if  $E' \in S$  then  $E \in S$ .

*Proof.* First, BMM satisfies the two above properties. Now, let S be a set of well-formed executions satisfying both properties. We show that BMM  $\subseteq S$ . Let  $E \in \mathsf{BMM}$ . If E is SC, then  $E \in S$ . Otherwise, there exists an SC execution E' such that  $E \xrightarrow{RO} E'$ . But E' is in S, so E is in S too.

We use this lemma to show that BMM is a subset of the JMM executions and to show the equivalence between BMM and BMM<sub>o</sub>.

### 5.1 BMM is a Subset of JMM

The current Java Memory Model defines the set of legal executions as a subset of all well-formed executions that are justifiable using a sequence of intermediate justifications. In order to connect our model with the JMM, rather than unfolding the details of this formal definition, we rely on the following JMM properties:

- JMM accepts all sequentially consistent executions,

- JMM allows reordering of non-volatile memory accesses hitting different locations [34].

THEOREM 5.2. Let JMM be the set of all legal executions permitted by the JMM. Then, BMM  $\subseteq$  JMM.

*Proof.* We use here Lemma 5.1. We first know that JMM contains all SC executions. Then, suppose that  $E \xrightarrow{RO} E'$  with  $E' \in \text{JMM}$ . In the JMM, reordering non volatile memory accesses hitting different addresses is allowed [34]. We use this property to un-transform E' into E. Hence, E is also in JMM, meaning that JMM is backward-closed by WR\*R.

### 5.2 DRF Guarantee

We establish that BMM enjoys the important property that any reasonable memory model should have, namely a *data-race-free guarantee* - data-race free programs have SC executions only. We first define the standard notions of concurrent conflicting memory action, data-race, and data-race-free programs:

DEFINITION 5.5 (Conflicting actions). Two non-volatile actions  $a,b \in \mathbb{A}_r \cup \mathbb{A}_w$  are conflicting if they target the same address and  $T(a) \neq T(b)$  and at least one of them is a write.

DEFINITION 5.6 (Data-races). Let  $\langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle$  be a BMM SC execution. Two conflicting actions a, b form a data-race if they are not ordered by  $\xrightarrow{hb}$ .

DEFINITION 5.7 (DRF). A program P is data-race free, written DRF(P), if all of its SC executions are free of data-race.

THEOREM 5.3 (DRF guarantee). For all P, if DRF(P), then for all execution  $E \in \mathsf{BMM}(P)$ , E is SC.

*Proof.* Let P be such that DRF(P), and  $E \in \mathsf{BMM}(P)$ . By Theorem 5.2,  $E \in \mathsf{JMM}(P)$ . But JMM satisfies the DRF guarantee [32], so E is sequentially consistent.

# 6. BMM<sub>o</sub>: An Operational Memory Model

In this section, we provide an operational view of the BMM. The reorderings allowed in its axiomatic version can be implemented by a BMM<sub>o</sub> machine that attaches a write-buffer to each running thread. The BMM<sub>o</sub> semantics is also parametrized by an intra-thread semantics. Hence, we need to consider an extra set of actions: the

$$\frac{ts(t) \stackrel{\tau}{\longrightarrow} s}{ts, b, m \stackrel{\tau_t}{\longrightarrow} ts[t \mapsto s], b, m} [\text{Tau}]$$

$$\frac{ts(t) \stackrel{r_t^i x \mid V(w)}{\longrightarrow} s \quad w = \text{rd}_t(b, m, x) \quad \neg \text{volatile}(x)}{ts, b, m \stackrel{r_t^i x \mid w}{\longrightarrow} ts[t \mapsto s], b, m} [\text{Read}]$$

$$\frac{ts(t) \stackrel{w_t^i x, v}{\longrightarrow} s \quad \neg \text{volatile}(x)}{ts, b, m \stackrel{w_t^i x, v}{\longrightarrow} ts[t \mapsto s], b[t \mapsto (w_t^i x, v) ::: b(t)], m} [\text{Write}]$$

$$\frac{b(t) = l \cdot [w_t^i x, v]}{ts, b, m \stackrel{\overline{\boxtimes}(w_t^i x, v)}{\longrightarrow} ts, b[t \mapsto l], m[x \mapsto (w_t^i x, v)]} [\text{UnBuff}]$$

$$\frac{ts, m \stackrel{\lambda}{\longrightarrow}_{\text{synch}} ts', m' \quad b(t) = []}{ts, b, m \stackrel{\lambda}{\longrightarrow} ts', b, m'} [\text{Synch}]$$

Figure 6. BMM<sub>o</sub> machine (labelled transition system).

silent actions in  $\mathbb{A}_{sil}$  that are either the unbuffering  $\overline{\mathbb{B}}(a)$  of a write action  $a \in \mathbb{A}_w \setminus \mathbb{A}_d$  by thread T(a) or a silent step  $\tau_t$  by thread t.

$$\mathbb{A}_{\mathrm{sil}} ::= \overline{\mathrm{B}}(a) \mid \tau_t$$

The idea behind BMM<sub>o</sub> is to provide a generative, operational machine that executes an input operational execution, modifying a memory state, made of thread buffers and a shared memory. The input of the BMM<sub>o</sub> machine is an operational execution, made of a program and a trace of *operational actions*. An operational action  $a \in \mathbb{A}_{op}$  is either an action in  $\mathbb{A} \setminus (\mathbb{A}_d \cup \mathbb{A}_r)$ , or a pair in  $\mathbb{A}_r \times \mathbb{A}_w$  (for each read action we record the write action that it sees, and refer to it as its *write-seen*), or a silent action in  $\mathbb{A}_{sil}$ .

DEFINITION 6.1 (Operational execution). An operational execution is a pair (P, tr) where P is a program and  $tr \in \operatorname{list}(\mathbb{A}_{\operatorname{op}})$  is finite and such that no action appear more than once in tr.

The  $BMM_o$  machine is then defined by a transition system, parametrized by an intra-thread semantics. We now describe its states and transitions. A  $BMM_o$  state  $\in$  State is a record

$$\begin{array}{cccc} ts & \in & \mathbb{T} \rightharpoonup \mathrm{State_{intra}}; & \text{(intra-thread state of threads)} \\ b & \in & \mathbb{T} \rightharpoonup \mathrm{list}(\mathbb{A}_{\mathrm{w}} \setminus \mathbb{A}_{\mathrm{d}}); & \text{(one buffer per thread)} \\ m & \in & \mathbb{X} \rightarrow \mathbb{A}_{\mathrm{w}} & \text{(one write action per address)} \end{array}$$

The state first keeps track of each intra-thread state in  $State_{intra}$ . Each thread is given a write buffer; all non-volatile write actions are first written to this buffer. When unbuffered, these writes are committed to the shared memory m, that maps addresses to write actions. Given a memory state (buffers b and memory m), the BMM $_o$  machine specifies the write action a thread t can read when accessing the address x:

$$\mathrm{rd}_t(b,m,x) = \begin{cases} w & \text{if } w \text{ is the first write to } x \text{ in } b(t) \\ m(x) & \text{if there is no write to } x \text{ in } b(t) \end{cases}$$

If a pending write to this address appears in the buffer of t, we take the most recent in the execution (*i.e.* the first in the buffer). Otherwise we consult the memory. If no write has been performed yet at this address we will retrieve the default value for this address.

The BMM<sub>o</sub> machine is defined as a labeled transition system where steps are labeled by operational actions. The salient semantic rules are given Fig. 6. In all rules (except BUFF) the BMM<sub>o</sub> machine makes a step that the intra-thread semantics can match. Rule TAU corresponds to a intra-thread silent step (when e.g. the thread operates on registers). The BMM<sub>o</sub> memory state does not change in this case. On a non-volatile read (READ) the value is obtained from

Figure 7. BMM<sub>o</sub> machine (synchronization actions).

the memory state using the rd function. For this action, the intrathread event is a pair  $r_t^i x \mid v$  composed of a read and a value. The intra-thread semantics accepts any value here but the purpose of the rule is to constrain it using thread-local buffers and shared memory. On a non-volatile write (WRITE), the write action is put onto the thread's buffer. A write action can be unbuffered at any time, in which case the write is committed into shared memory (UNBUFF). All synchronizing actions are emitted by threads whose buffers are empty. They are gathered under the SYNCH rule whose definition (relying on a relation  $\rightarrow_{synch}$ ) is in Fig. 7. Reads from and writes to volatile locations directly access the memory so that all threads have a consistent view (READV and WRITEV). When a thread ends (END), its state is kept in the BMMo state, enabling other threads to join it (JOIN), and preventing it to from being restarted (SPAWN).

We then define a BMM<sub>o</sub> execution as a constrained operational execution that is accepted by the BMM<sub>o</sub> machine: the input trace is properly locked and can be executed by the machine, with the intended meaning that the input execution is intra-thread consistent.

DEFINITION 6.2 (BMM<sub>o</sub> execution). An operational execution (P, tr) is in BMM<sub>o</sub>(P) if there exists states  $s_0, s_1, \ldots, s_n$  in State satisfying the following:

- tr is properly locked (see Definition 4.5, using  $\xrightarrow{tr}$  instead of  $\xrightarrow{po}$  and  $\xrightarrow{so}$ ),

- $s_0$  is an initial state: the memory maps every address to the corresponding default write  $(\forall x, m(x) = w_0 x)$ , buffers are empty and  $s_0$  is defined for exactly one thread, mapping it to the Ready state,

- $tr = a_1 :: \cdots :: a_n \in \text{list}(\mathbb{A}_{\text{op}}),$

- for all  $i \in \{1, \ldots, n\}, s_{i-1} \xrightarrow{a_i} s_i$ .

The BMM $_{0}$  behaviors of program P are external action traces obtained by projecting all executions of P accepted by the BMM<sub>o</sub> machine on  $\mathbb{A}_{x}$ :

$$Obs_{o}(P) = \{ tr \downarrow_{\mathbb{A}_{v}} | (P, tr) \in \mathsf{BMM}_{o}(P) \}$$

# Equivalence of BMM and BMM<sub>o</sub>

We show that BMM and BMM<sub>o</sub> are equivalent relaxed memory models: they allow the exact same set of behaviors for any program.

Theorem 7.1. For all program

$$P$$

,  $Obs_o(P) = Obs(P)$ .

The proof relies on an operator  $\rho$  that bridges the gap between BMM and BMM<sub>o</sub> by building axiomatic executions from operational ones.

DEFINITION 7.1 ( $\rho$  operator). Let  $E_0 = (P, tr)$  be an execution,  $\rho$ is defined as  $\rho(E_0) = \langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle$  where

• A is the set of non-silent actions in tr,

- for all  $a, b \in A$ ,  $a \xrightarrow{po} b$  iff T(a) = T(b) and  $a \xrightarrow{tr} b$ .

- for all  $a, b \in A$ ,  $a \xrightarrow{so} b$  iff  $a, b \in \mathbb{A}_s$  and  $a \xrightarrow{tr} b$ ,

- for all pairs  $\mathbf{r}_t^i x \mid w$  in tr,  $W(\mathbf{r}_t^i x) = w$ .

We show that  $\rho(BMM_0) = BMM$ . Each inclusion is proved and Theorem 7.1 follows from the following lemma.

LEMMA 7.2. Let

$$E_o = (P, tr)$$

be an operational execution and  $\langle P, A, \xrightarrow{po}, \xrightarrow{so}, W \rangle = \rho(E_o)$ , then  $tr \downarrow_{\mathbb{A}_v} = (\xrightarrow{so} \downarrow_{\mathbb{A}_v})$ .

*Proof.* By definition of  $\rho$ , we know that for all  $a, b \in A$ ,  $a \xrightarrow{so} b$  iff  $a, b \in \mathbb{A}_s$  and  $a \xrightarrow{tr} b$ .

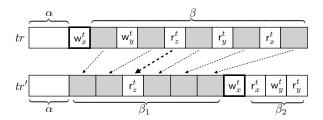

We define auxiliary notions needed for the proof. An operational execution  $E_o$  is well-formed if  $\rho(E_o)$  is well-formed, and it is  $SC_{\rho}$  if  $\rho(E_{o})$  is SC. Similarly, we define operational reorderings relying on  $\rho$ : an execution  $E'_o$  is an operational reordering of  $E_o$  if  $\rho(E_o) \xrightarrow{\mathrm{WR}^*\mathrm{R}} \rho(E'_o)$ . We abuse notations and write it  $E_o \xrightarrow{\mathrm{WR}^*\mathrm{R}} E'_o$ , and lift this notion to trace reorderings  $\xrightarrow{RO}$ . To lighten the notations in this section, we keep implicit the unique identifier of actions and write  $w_x^t$  for  $w_t^i x, v$  (the value written is omitted). When considering operational actions in a trace we generally omit the write action w attached to a read action.

# **7.1** $\rho(\mathsf{BMM}_{\mathsf{o}}) \subset \mathsf{BMM}$

We prove that every BMM<sub>o</sub> execution trace can be reordered into a SC trace. The proof relies on a reordering scheme explained in the following lemma.

LEMMA 7.3. Let  $E_o = (P, tr) \in BMM_o(P)$ , with  $tr = \alpha \cdot [\mathbf{w}_x^t] \cdot \beta$ an execution such that  $\overline{B}(w_x^t) \notin \beta$ . We write

- $\mathcal{W}^t = \{ \mathbf{w}_y^t \in \beta \mid y \in \mathbb{X} \}$ , write actions belonging to thread t,  $\mathcal{R}^t = \{ \mathbf{r}_y^t \in \beta \mid \mathbf{w}_x^t \cdot \beta = \gamma_1 \cdot \mathbf{w}_y^t \cdot \gamma_2 \cdot \mathbf{r}_y^t \cdot \gamma_3, \ y \in \mathbb{X}, \ \gamma_1, \gamma_2, \gamma_3 \in \text{list}(\mathbb{A}_{\text{op}}) \}$ , read actions seeing a write performed by t in  $[\mathbf{w}_x^t] \cdot \beta$ ,

- $\beta \setminus (\mathcal{W}^t \cup \mathcal{R}^t)$  the remaining actions in  $\beta$ .

Then, there exist  $P', \beta_1, \beta_2$  such that  $E'_{o} = (P', tr') \in \mathsf{BMM}_{o}(P')$ ,  $E_{\circ} \xrightarrow{RO} E'_{\circ}$  and  $tr' = \alpha \cdot \beta_1 \cdot [\mathbf{w}_x^t] \cdot \beta_2$  where,

- $\beta_1 = \beta \downarrow_{\beta \setminus (\mathcal{W}^t \cup \mathcal{R}^t)}$ ,

- $\beta_2$  contains the elements of  $\mathcal{W}^t \cup \mathcal{R}^t$ ,

- $[\mathbf{w}_x^t] \cdot \beta_2$  matches the pattern  $(\mathbf{w}_{x_1}^t; (\mathbf{r}_{x_1}^t)^*) \cdot \ldots \cdot (\mathbf{w}_{x_n}^t; (\mathbf{r}_{x_n}^t)^*)$ ,

- for all  $\delta$ ,  $(P, tr \cdot \delta) \in \mathsf{BMM}_{\mathsf{o}}(P)$  then  $(P', tr' \cdot \delta) \in \mathsf{BMM}_{\mathsf{o}}(P')$ .

Before going into the detail of the proof, we give an intuition on how we use it. This lemma is applied to a part of an execution in which a write action, performed by t, stays in its buffer. This is illustrated in the following figure, where the grey regions denote subsequences of actions whose owning thread is not t. The bold stroke action  $w_x^t$  is

the write action that remains in t's buffer until the end of tr. We will use this action as a pivot on all the actions performed in the rest of tr, so that the resulting trace tr' is as illustrated: (a) all grey actions are shifted before the pivot, remaining in the same relative order, by changing the interleaving; (b) actions of thread t are handled with the  $WR^*R$  reordering rule. Because write actions of t cannot be moved, they are kept to the right of the pivot.

Handling read actions of t is more involved: either they see a write that occurred (necessarily in thread t) after the pivot in tr, and they are accumulated in a pattern  $(\mathbf{w}_{x_1}^t; (\mathbf{r}_{x_1}^t)^*) \cdot \ldots \cdot (\mathbf{w}_{x_n}^t; (\mathbf{r}_{x_n}^t)^*)$ , or they see a write that occurs before the pivot, and  $\mathbf{WR}^*\mathbf{R}$  is applied repeatedly on this pattern, until they are swapped before  $\mathbf{w}_x^t$ .

*Proof.* Let  $E_o = (P, tr) \in \mathsf{BMM}_o(P)$ , with  $tr = (\alpha \cdot [\mathsf{w}_x^t] \cdot \beta)$  and  $\overline{\mathsf{B}}(\mathsf{w}_x^t) \not\in \beta$ . The sub-trace  $[\mathsf{w}_x^t] \cdot \beta$  can be decomposed as  $[\mathsf{w}_x^t] \cdot \beta = \beta_p \cdot \beta_t$  with  $\beta_p = [\mathsf{w}_y^t; (r_y^t)^*]^+$  (we take the shortest  $\beta_t$ ). We now proceed by induction on the length of  $\beta_t$ .

- Base case: β<sub>t</sub> is empty. We don't need any reordering transformation to reach the expected pattern.

- Inductive case. We proceed by case analysis on the first element of β<sub>t</sub> = a :: β'<sub>t</sub> and show that a can be either (i) integrated inside the pattern β<sub>p</sub> or (ii) be moved before this pattern:

- If  $a=\mathbf{r}_k^t$ , when k is one of the addresses of  $\beta_p$ . Here, we integrate in  $\beta_p$  by applying an WR\*R as many times as needed to make it part of the right  $\mathbf{w}_k^t(\mathbf{r}_k^t)^*$  pattern such that  $\beta_p=\beta_{p_1}\cdot(\mathbf{w}_k^t(\mathbf{r}_k^t)^*)\cdot\beta_{p_2}$ . Note WR\*R can be applied because the pattern only concerns thread t, and the visibility conditions required by WR\*R are fulfilled. The right-most such pattern before a, i.e. such that there is no  $\mathbf{w}_k^t$  in  $\beta_{p_2}$ , is the only one that can ensure the write-seen of a to be preserved, according to BMM<sub>o</sub>. Thus the resulting trace  $(P', \alpha \cdot \beta_{p_1} \cdot (\mathbf{w}_k^t(\mathbf{r}_k^t)^*a) \cdot \beta_{p_2} \cdot \beta_t')$  is BMM<sub>o</sub>.

- If  $a = r_k^t$ , when k is not any of the addresses of  $\beta_p$ . We apply the same reasoning as in the previous case, rewriting the trace with WR\*R, but in this case, this simply amounts to put a before  $w_x^t$ , because WR\*R will be applied on the whole  $\beta_p$  (and the write-seen is trivially kept valid).

- If  $a=\overline{\mathbb{B}}(a')$ , then  $a'\in\alpha$  because there is no unbuffering action in  $\beta_p$ . This unbuffering could have been done just before  $\mathbf{w}_x^t$ . This unbuffering does not modify the visibility constraints of the new trace, as it cannot overwrite any of the write actions in  $\beta_p$ . For any trace  $\delta$ , if  $(P,\alpha\cdot\beta_p\cdot[a]\cdot\beta_t'\cdot\delta)\in\mathsf{BMM}_0(P)$  then the trace  $(P,\alpha\cdot[a]\cdot\beta_p\cdot\beta_t'\cdot\delta)$  is also in  $\mathsf{BMM}_0(P)$ : any read in  $\delta$  that sees a' in the first trace can still see it in the second trace because no write action in  $\beta_p$  is unbuffered before  $\delta$ .

- because no write action in  $\beta_p$  is unbuffered before  $\delta$ .

For all other cases  $(a = \mathsf{r}_k^{t''}, \text{ where } t'' \neq t, \, a = \mathsf{w}_k^{t''}, \text{ with } t'' \neq t, \text{ and } a \in \mathbb{A}_s)$ , we can just change the interleaving to move a before  $\beta_p$  and conclude easily.

For each resulting trace, we show that we are under the induction hypothesis premises. Hence, we conclude by induction.

This reordering scheme is extensively used for proving Lemma 7.4, stating that the reordering interpretation of BMM can be simulated in the operational world.

LEMMA 7.4. Let  $E_o = (P, tr) \in \mathsf{BMM}_o(P)$ . Then there exist P', tr' such that  $E_o \xrightarrow{RO} (P', tr')$ , with  $(P', tr') \in \mathsf{BMM}_o(P')$  is  $\mathrm{SC}_o$ .

In order to prove the lemma by induction, we need to prove a stronger result, that includes an additional property on the shape of the two operational traces tr and tr'. This so-called *write-swapping* property is formally defined as follows.

DEFINITION 7.2 (Write-swapping). Let tr and tr' two sequences of actions. The write-swapping property holds on (tr, tr') if for any write actions  $w_1, w_2$  to the same address,

- if  $w_1 \xrightarrow{tr} w_2$  and  $w_2 \xrightarrow{tr'} w_1$  (write actions have been swapped) then the trace tr is of the form  $tr = \alpha \cdot [w_1] \cdot \beta \cdot [w_2] \cdot \gamma$  and  $\overline{B}(w_1) \notin \beta$ .

- if  $w_1 \xrightarrow{tr} w_2$  and  $w_1 \xrightarrow{tr'} w_2$  (write actions have not been swapped) then if  $\overline{B}(w_1)$  occurs before  $w_2$  in tr, it is also the case in tr'.

*Proof.* We prove Lemma 7.4 by strong induction on the size of the execution |tr| = n. Assume the property holds for any integer k < n. Let  $E_o = (P, tr) \in \mathsf{BMM}_o(P)$  an execution of size n.

We assume n>0 (the case n=0 holds trivially). So tr is of the form  $tr=tr_1\cdot [a]$ . By induction on  $tr_1$ , we get  $P_2$  and  $tr_2$  such that  $(P,tr_1)\stackrel{RO}{\longrightarrow} (P_2,tr_2)$ , with  $E_{\rm o}^2=(P_2,tr_2)\in {\sf BMM_o}(P_2)\cap {\sf SC}_{\rho}$ , plus a write-swapping on  $(tr_1,tr_2)$ .

We extend  $E_o^2$  to  $(P_2, tr_2 \cdot [a])$ . If action a is not a read action, we can conclude directly. Otherwise,  $a = r_x^{t_3}$ , the extended trace is in  $\mathsf{BMM}_o(P_2)$ , and the write-swapping property holds. It remains to show that it is  $\mathsf{SC}_\rho$ . If it is not, we proceed by case analysis:

Case 1: There is a thread  $t \neq t_3$  whose buffer is not empty at the end of  $tr_2$ . Formally, there is a write action  $\mathbf{w}_y^t$  in  $tr_2$  such that  $\overline{\mathbf{B}}(\mathbf{w}_y^t) \not\in tr_2$ .  $tr_2$ . [a] is of the form  $\alpha \cdot [\mathbf{w}_y^t] \cdot \beta \cdot [\mathbf{r}_x^{t_3}]$ . Applying Lemma 7.3 on  $\mathbf{w}_y^t$ , we get  $P_3$  and  $tr_3$  such that  $(P_2, tr_2. [a]) \xrightarrow{RO} (P_3, tr_3)$  with  $E_o^3 = (P_3, tr_3) \in \mathrm{BMM}_o(P_3)$  and  $tr_3 = \alpha \cdot \beta_1 \cdot [\mathbf{r}_x^{t_3}] \cdot [\mathbf{w}_y^t] \cdot \beta_2$  with  $[\mathbf{w}_y^t] \cdot \beta_2$  matching the pattern  $[\mathbf{w}^t; (\mathbf{r}^t)^*]^+$ . By induction on  $\alpha \cdot \beta_1 \cdot [\mathbf{r}_x^{t_3}]$ , we get  $P_4$  and  $tr_4$  such that  $(P_3, \alpha \cdot \beta_1 \cdot [\mathbf{r}_x^{t_3}]) \xrightarrow{RO} (P_4, tr_4)$ , with  $E_o^4 = (P_4, tr_4) \in \mathrm{BMM}_o(P_4) \cap \mathrm{SC}_\rho$ , plus a write-swapping property on the traces. We concatenate the suffix  $[\mathbf{w}_y^t] \cdot \beta_2$  to extend  $tr_4$  to an execution in  $\mathrm{BMM}_o(P_4) \cap \mathrm{SC}_\rho$ . The sequential consistency holds thanks to the pattern of  $[\mathbf{w}_y^t] \cdot \beta_2$ . The write-swapping is preserved by the concatenation.

Case 2: All threads distinct from  $t_3$  have their buffer empty at the end of  $tr_2$ . Formally, for every write action  $\mathbf{w}_y^t \in tr_2$  such that  $t \neq t_3$ ,  $\overline{\mathbf{B}}(\mathbf{w}_y^t) \in tr_2$ . Let  $\mathbf{w}_x^{t_1}$  be the write seen by  $\mathbf{r}_x^{t_3}$ .

- If  $\overline{\mathrm{B}}(\mathsf{w}_x^{t_1}) \not\in tr_2$ , it means that  $t_1 = t_3$ . The trace  $tr_2.[a]$  is of the form:  $\alpha \cdot [\mathsf{w}_x^{t_1}] \cdot \beta \cdot [\mathsf{r}_x^{t_3}]$ . We apply Lemma 7.3 on  $\mathsf{w}_x^{t_1}$ . The trace  $\alpha \cdot \beta_1 \cdot [\mathsf{w}_x^{t_1}] \cdot \beta_2$  we obtain is in BMMo and by the shape of  $\beta_1$  and  $\beta_2$  it is  $\mathrm{SC}_\rho$ . We must show  $\mathsf{w}_x^{t_1}$  is now the most recent write to x in  $\beta_2$ . But any other write there would be from thread  $t_1$  and  $r_x^{t_3}$  could thus not see  $\mathsf{w}_x^{t_1}$ .

- If  $\overline{\mathrm{B}}(\mathsf{w}_x^{t_1}) \in tr_2$ , then the trace  $tr_2.[a]$  is of the form  $\alpha \cdot [\mathsf{w}_x^{t_1}] \cdot \beta \cdot [\overline{\mathrm{B}}(\mathsf{w}_x^{t_1})] \cdot \gamma \cdot [\mathsf{r}_x^{t_3}]$ . No  $\mathsf{w}_x^{t_2}$  more recent than  $\mathsf{w}_x^{t_1}$  can appear in  $\gamma$ : either it is unbuffered in  $\gamma$  and it would overwrite  $\mathsf{w}_x^{t_1}$  or it is not unbuffered but then  $t_2 = t_3$  and  $\mathsf{w}_x^{t_1}$  could not be seen by  $\mathsf{r}_x^{t_3}$ . No unbuffering  $\overline{\mathrm{B}}(\mathsf{w}_x^{t_2})$  can either appear in  $\gamma$  since it would overwrite  $\mathsf{w}_x^{t_1}$ .

By Lemma 7.3 on  $\mathbf{w}_x^{t_1}$  and  $\beta$ , we get a trace  $tr_3$  such that  $tr_3 \cdot [\overline{\mathbf{B}}(\mathbf{w}_x^{t_1})] \cdot \gamma \cdot [\mathbf{r}_x^{t_2}] = \alpha \cdot \beta_1 \cdot [\mathbf{w}_x^{t_1}] \cdot \beta_2 \cdot [\overline{\mathbf{B}}(\mathbf{w}_x^{t_1})] \cdot \gamma \cdot [\mathbf{r}_x^{t_2}]$ . In this trace, the most recent write to x is now  $\mathbf{w}_x^{t_1}$ . The subtrace  $\alpha \cdot \beta_1 \cdot [\mathbf{w}_x^{t_1}] \cdot \beta_2 \cdot [\overline{\mathbf{B}}(\mathbf{w}_x^{t_1})]$  is SC because  $\alpha \cdot [\mathbf{w}_x^{t_1}] \cdot \beta \cdot [\overline{\mathbf{B}}(\mathbf{w}_x^{t_1})]$  was. It remains to show that all reads in  $\gamma$  still see the most recent writes. By induction on  $tr_3 \cdot [\overline{\mathbf{B}}(\mathbf{w}_x^{t_1})] \cdot \gamma$ , an SC execution is rebuilt, that keeps the same write-seen.

Finally, we obtain the first inclusion as a corollary of Lemma 7.4.

COROLLARY 7.5.  $\rho(\mathsf{BMM}_{\mathsf{o}}) \subset \mathsf{BMM}$ .

*Proof.* Let  $E_o = (P, tr) \in \mathsf{BMM}_o(P)$ . By Lemma 7.4, we have  $E_o \xrightarrow{RO} E_o'$ , with  $E_o' = (P', tr') \in \mathsf{BMM}_o(P')$  is  $\mathrm{SC}_\rho$ . By definition,  $\rho(E_o) \xrightarrow{RO} \rho(E_o')$  and  $\rho(E_o')$  is SC. Hence,  $\rho(E_o) \in \mathsf{BMM}(P)$ .

#### **7.2** BMM $\subseteq \rho(BMM_0)$

We use here the post-fixpoint characterization of BMM (Lemma 5.1). We first show that  $\rho(\mathsf{BMM_o})$  contains all SC axiomatic executions. Let  $E = \langle P, A, \stackrel{po}{\longrightarrow}, \stackrel{so}{\longrightarrow}, W \rangle \in \mathsf{BMM}$  be an SC execution. Then there exists a total order  $\stackrel{to}{\longrightarrow}$  on A, compatible with  $\stackrel{po}{\longrightarrow}$  and  $\stackrel{so}{\longrightarrow}$  such that all read actions in A see the last write to their address w.r.t.  $\stackrel{to}{\longrightarrow}$ . We claim that  $E_o = (P, tr)$  can be build, with  $tr \downarrow_A = \stackrel{to}{\longrightarrow}$ , and that  $E_o \in \mathsf{BMM_o}(P)$ . Silent actions are inserted in  $\stackrel{to}{\longrightarrow}$  so that each write action is immediately unbuffered, and that tr is intra-thread consistent – an equivalent condition was required for  $E \in \mathsf{BMM}(P)$ . Finally  $\rho(E_o) = E$ . We also show that  $\rho(\mathsf{BMM_o})$  is backward-closed by WR\*R. Let E and E' two well-formed axiomatic executions such that  $E' \in \rho(\mathsf{BMM_o})$  and  $E \stackrel{\mathrm{WR*R}}{\longrightarrow} E'$ .  $E' \in \rho(\mathsf{BMM_o})$  so there exists  $E'_o \in \mathsf{BMM_o}$  such that  $E' = \rho(E'_o)$ . WR\*R is a valid transformation under  $\mathsf{BMM_o}$  (see Sec. 8.1), meaning that there exists  $E_o \in \mathsf{BMM_o}$  such that  $\rho(E_o) = E$ . Hence,  $E \in \rho(\mathsf{BMM_o})$ .

# 8. Validity of Transformations

One of the objectives of any memory model is to take into account the reorderings performed by the hardware and to allow compilers to perform some program transformations that deal directly with memory accesses or locks. Tab. 2 gives standard transformations and their validity under various memory models [32, 34].

For a proof of validity we rely on the operational model: we consider a  $\mathsf{BMM}_\circ$  trace of a transformed program and show there exists a valid  $\mathsf{BMM}_\circ$  trace of the original program with the same behavior. For a proof of invalidity, we provide a counter-example and use the intuitive reordering memory model of  $\mathsf{BMM}$ : given a program P and a transformed program P', we show that there exists an execution that is valid for P' but invalid for P (both under  $\mathsf{BMM}$ ). This table demonstrate that, despite its restricted set of reorderings,  $\mathsf{BMM}$  allows useful transformations.

#### 8.1 Validity of WR and $WR^*R$

Among the set of transformations, the validity of the local reordering  $WR^*R$  is crucial for the memory model inclusion.

DEFINITION 8.1 (Valid reordering). A local reordering  $\stackrel{\Phi}{\rightarrow}$  between axiomatic executions is said to be valid with respect to BMM<sub>o</sub> if for all axiomatic execution E and all operational execution  $E_o$ ,  $E \stackrel{\Phi}{\rightarrow} \rho(E_o)$  and  $E_o \in BMM_o$  implies that there exists  $E'_o \in BMM_o$  such that  $E = \rho(E'_o)$ .

We can show that both WR and WR\*R are valid.

| Transformation                           | SC.          | JMM          | ВММ          |

|------------------------------------------|--------------|--------------|--------------|

| Trace preserving transformation          | <b>√</b>     | <b>√</b>     | <b>√</b>     |

| Reordering normal memory accesses        | ×            | $\checkmark$ | $\otimes$    |

| Redundant read after read elimination    | $\checkmark$ | ×            | $\checkmark$ |

| Redundant read after write elimination   | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Irrelevant read elimination              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Irrelevant read introduction             | $\checkmark$ | ×            | $\checkmark$ |

| Redundant write before write elimination | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Redundant write after read elimination   | $\checkmark$ | ×            | ×            |

| Roach motel reordering                   | $\checkmark$ | ×            | $\otimes$    |

We write  $\checkmark$  for a valid transformation and  $\times$  when it is generally wrong,  $\otimes$  for limited applicability: only WR\*R applies to normal memory accesses; a read can be delayed past a lock and a write can take over an unlock.

**Table 2.** Validity of transformations in memory models.

LEMMA 8.1.  $\xrightarrow{\text{WR}}$  is valid.

П

Proof. Let  $E = \langle P, A, \stackrel{po}{\longrightarrow}, \stackrel{so}{\longrightarrow}, W \rangle$  be an axiomatic execution and  $E_o = (P', tr')$  an operational execution with  $E \xrightarrow{\mathrm{WR}} \rho(E_o)$  and  $E_o \in \mathrm{BMM_o}$ . By hypothesis, we know that  $tr' = \beta \cdot [r_t^j x] \cdot \gamma \cdot [w_t^i y, v] \cdot \delta$  and  $\gamma$  does not contain any action owned by t except some unbuffering actions. The write action  $w_t^i y, v$  can be performed just after  $r_t^j x$  since the unbuffering in  $\gamma$  are independent of it and no read action in  $\gamma$  can see  $w_t^i y, v$  (it is still in its buffer). Hence the trace  $\beta \cdot [r_t^j x] \cdot [w_t^i y, v] \cdot \gamma \cdot \delta$  is still in  $\mathrm{BMM_o}$  for the same value-seen and write-seen information. After a swap we obtain a trace  $tr'' = \beta \cdot [w_t^i y, v] \cdot [r_t^j x] \cdot \gamma \cdot \delta$  that belongs to  $\mathrm{BMM_o}(P)$  (by definition of  $\stackrel{\mathrm{WR}}{\longrightarrow}$ ) and  $\rho(P, tr'') = E$ .

LEMMA 8.2.  $\xrightarrow{WR^*R}$  is valid.

Proof. Let  $E=\langle P,A,\stackrel{po}{\longrightarrow},\stackrel{so}{\longrightarrow},W\rangle$  be an axiomatic execution and let  $E_o=(P',tr')$  be an operational execution such that  $E\xrightarrow{\mathrm{WR}^*\mathrm{R}}\rho(E_o)$  and  $E_o\in\mathsf{BMM_o}$ . By hypothesis, the traces tr' is of the form  $tr'=\beta\cdot[r_t^jx]\cdot\gamma\cdot[\mathbf{w}_t^iy,v]\cdot\gamma_1\cdot[r_t^{i_1}y]\cdots\gamma_n\cdot[r_t^{i_n}y]\cdot\delta$ . Each  $\gamma,\gamma_1,\ldots,\gamma_n$  does not contain any action owned by t except some unbuffering actions. As in the previous proof, the action  $\mathbf{w}_t^iy,v$  can be performed just after  $r_t^jx$ . All read actions  $r_t^{i_1}y,\ldots,r_t^{i_n}y$  see the write  $\mathbf{w}_t^iy,v$  in tr' and can thus also be performed earlier. The trace  $\beta\cdot[r_t^jx]\cdot[\mathbf{w}_t^iy,v]\cdot[r_t^{i_1}y]\cdots[r_t^{i_n}y]\cdot\gamma\cdot\gamma_1\cdots\gamma_n\cdot\delta$  is still in  $\mathsf{BMM_o}(P')$  for the same value-seen and write-seen (the moved reads see  $\mathbf{w}_t^iy,v$  directly from t's buffer). We then conclude with a swap: the trace  $tr''=\beta\cdot[\mathbf{w}_t^iy,v]\cdot[r_t^{i_1}y]\cdots[r_t^{i_n}y]\cdot[r_t^{i_n}y]\cdot\gamma\cdot\gamma_1\cdots\gamma_n\cdot\delta$  belongs to  $\mathsf{BMM_o}(P)$  and  $\rho(P,tr'')=E$ .

#### 8.2 Other Valid Transformations

Given E' = (P', tr'), for each transformation we observe the shape of tr' and provide a corresponding BMM<sub>o</sub> trace of an untransformed program. We assume that the intra-thread semantics accepts the transformation. All read and write actions are non-volatile.

#### Redundant Read after Read Elimination.

$$tr' = \beta \cdot [\mathbf{r}_t^i x] \cdot \gamma$$

Trace  $\beta \cdot [\mathbf{r}_t^i x] \cdot [\mathbf{r}_t^j x] \cdot \gamma$  is in BMM<sub>o</sub>.  $\mathbf{r}_t^j x$  and  $\mathbf{r}_t^i x$  see the same write.

# Redundant Read after Write Elimination.

$$tr' = \beta \cdot [\mathbf{w}_t^i x, v] \cdot \gamma$$

Trace  $\beta \cdot [\mathbf{w}_t^i x, v] \cdot [\mathbf{r}_t^j x] \cdot \gamma$  is in BMM<sub>o</sub>.  $\mathbf{r}_t^j x$  sees  $\mathbf{w}_t^i x, v$  in its buffer.

#### Irrelevant Read Elimination.

$$tr' = \beta \cdot \delta$$

Trace  $\beta \cdot [\mathbf{r}_t^i x] \cdot \gamma$  is in BMM<sub>o</sub>.  $\mathbf{r}_t^i x$  sees the first write to x in the buffer or pick the current write attached to x in memory.

# Irrelevant Read Introduction.

$$tr' = \beta \cdot [\mathbf{r}_t^i x] \cdot \delta$$

Trace  $\beta \cdot \gamma$  is in BMMo. The visibility of the other actions is preserved.

# Redundant Write before Write Elimination.

$$tr' = \beta \cdot [\mathbf{w}_t^j y, v] \cdot \gamma$$

We distinguish two cases. If  $\gamma=\gamma_1\cdot\overline{\mathrm{B}}(\mathsf{w}_t^jy,v)\cdot\gamma_2$ . The trace  $\beta\cdot[\mathsf{w}_t^iy,v']\cdot[\mathsf{w}_t^jy,v]\cdot\gamma_1\cdot\overline{\mathrm{B}}(\mathsf{w}_t^iy,v')\cdot\overline{\mathrm{B}}(\mathsf{w}_t^jy,v)\cdot\gamma_2$  is in BMM<sub>o</sub>. Adding the unbuffering preserves the visibility of  $\mathsf{w}_t^jy,v$  since  $\mathsf{w}_t^iy,v'$  is never seen. Otherwise,  $\overline{\mathrm{B}}(\mathsf{w}_t^jy,v)\not\in\gamma$ . The trace  $tr'=\beta\cdot[\mathsf{w}_t^iy,v']\cdot[\mathsf{w}_t^jy,v]\cdot\gamma$  is in BMM<sub>o</sub>.  $\mathsf{w}_t^iy,v'$  is never seen.

**Roach-motel: Read-lock Reordering.** A read before a lock can be reordered (no action emitted by the thread t in  $\gamma$ ).

$$tr' = \beta \cdot [\mathbf{I}_t^i l] \cdot \gamma \cdot [\mathbf{r}_t^j x] \cdot \delta$$

We assume tr' is properly locked so no synchronization action on l is in  $\gamma$ . Hence the following interleaving is a valid trace of the transformed program:  $\beta \cdot \gamma \cdot [l_t^i l] \cdot [r_t^j x] \cdot \delta$ . Then the trace  $\beta \cdot \gamma \cdot [r_t^j x] \cdot [l_t^i l] \cdot \delta$  is in BMM<sub>o</sub>.

**Roach-motel:** Unlock-write Reordering. A write after an unlock can be reordered. Since the buffer must be empty, the transformed trace has the following shape, where  $\mathbf{w}_t^i x, v$  is the last non silent action of thread t.

$$tr' = \beta \cdot [\mathbf{w}_t^i x, v] \cdot \gamma \cdot [\overline{\mathbf{B}}(\mathbf{w}_t^i x, v)] \cdot \delta \cdot [\mathbf{u}_t^j l] \cdot \eta$$

There is no action emitted by thread t in  $\gamma$  except some unbufferings. No action in  $\gamma$  emitted by the other threads can see the write  $\mathbf{w}_t^i x, v$ . Then, changing the scheduling, we can obtain the following BMMo traces:  $\beta \cdot \gamma \cdot [\mathbf{w}_t^i x, v] \cdot [\overline{\mathbf{B}}(\mathbf{w}_t^i x, v)] \cdot \delta \cdot [\mathbf{u}_t^j l] \cdot \eta$ . By hypothesis, there is no action emitted by the thread t in  $\delta$ ; besides there is no lock/unlock action on l in  $\delta$ . Therefore changing the scheduling again can lead to the following BMMo (properly locked) trace:  $\beta \cdot \gamma \cdot [\mathbf{w}_t^i t, v] \cdot [\overline{\mathbf{B}}(\mathbf{w}_t^i x, v)] \cdot [\mathbf{u}_t^j l] \cdot \delta \cdot \eta$ . Finally, the following trace is a BMMo execution of the untransformed program:  $\beta \cdot \gamma \cdot [\mathbf{u}_t^j l] \cdot [\mathbf{w}_t^i x, v] \cdot [\overline{\mathbf{B}}(\mathbf{w}_t^i x, v)] \cdot \delta \cdot \eta$ .

#### 8.3 Invalid Transformations

The BMM helps understand why some transformations are invalid.

**Redundant Write after Read Elimination.** Here v is volatile.

On the left, we see why the execution is not valid: it isn't SC and no reordering is possible. After the redundant write elimination, the execution becomes valid because the read  $r_3 \leftarrow x$  can be reordered with the write  $y \leftarrow 1$  to give a SC execution. This transformation thus introduced new behaviors.

# Roach-motel: Unlock-read Reordering.

Reordering reads and unlocks is not allowed. Here, the reads cannot both see the default writes, whereas they could if one of them was hoisted into the critical section and reordered with the preceeding write.

# $\begin{array}{c|c} x \leftarrow 0 & y \leftarrow 0 \\ \text{lock } l & \text{lock } l' \\ x \leftarrow 1 & \text{unlock } l \\ r_1 \leftarrow y & r_2 \leftarrow x \end{array}$

#### Roach-motel: Write-lock Reordering.

Reordering writes and locks is not allowed. The reads cannot both see the default writes, whereas they could if one of the writes was hoisted into the critical section and reordered with the next read.

| $x \leftarrow 0$   | $y \leftarrow 0$           |

|--------------------|----------------------------|

| $x \leftarrow 1$   | $y \leftarrow 1$           |

| lock $l$           | $y \leftarrow 1$ lock $l'$ |

| $r_1 \leftarrow y$ | $r_2 \leftarrow x$         |

| unlock $\it l$     | unlock $l'$                |

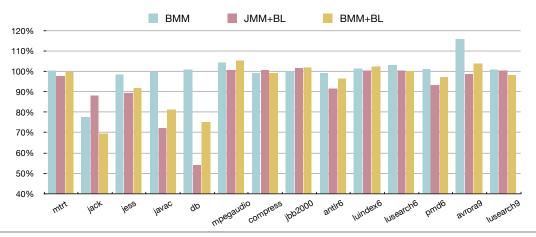

# 9. Empirical Evaluation of the BMM